# TROT: A Three-Edge Ring Oscillator Based True Random Number Generator With Time-to-Digital Conversion

Miloš Grujić<sup>10</sup> and Ingrid Verbauwhede<sup>10</sup>, *Fellow*, *IEEE*

Abstract—This paper introduces a new true random number generator (TRNG) based on a three-edge ring oscillator. Our design uses a new technique with a time-to-digital converter to effectively acquire jitter accumulated independently by each edge. As a part of the security evaluation, we present the stochastic model of the TRNG's digital noise source and estimate a lower bound of the min-entropy per random bit. Starting from the obtained entropy bound, we propose a procedure for selecting and implementing an area-efficient and throughput-optimal postprocessing function based on the best known linear codes that will increase the output min-entropy rate to more than 0.999. The proposed TRNG exquisitely balances low design effort and resource consumption with high throughput and a high minentropy rate, making it more suitable for randomness-demanding and resource-constrained platforms than the state-of-the-art. The complete implementation of the TRNG digital noise source and the post-processing occupies 33 slices and achieves a throughput of 12.5 Mbps on Xilinx Zynq-7000 FPGAs. The min-entropy of the generated random bits is assessed by NIST SP 800-90B entropy estimators, and the tested sequences pass the AIS-31 test suit.

*Index Terms*—Entropy, hardware security, multimode ring oscillator, post-processing, stochastic model, true random number generator (TRNG).

## I. INTRODUCTION

**R**ANDOM number generators are indispensable components of any modern security system. With physically unclonable functions (PUFs), true random number generators (TRNGs) are the only cryptographic primitives producing truly unpredictable bits for generating secrets in symmetricand public-key cryptography. Random number generators are also extensively used in various randomization-based countermeasures for protecting cryptographic implementations against

Manuscript received October 12, 2021; revised December 23, 2021 and February 7, 2022; accepted February 22, 2022. This work was supported in part by the CyberSecurity Research Flanders under Grant VR20192203, in part by the Research Council KU Leuven C1 under Contract C16/15/058, and in part by the European Commission through the Horizon 2020 Research and Innovation Program through QRANGE under Grant H2020-FETFLAG-2018-03-820405 and Cathedral European Research Council (ERC) Advanced under Grant 695305. This article was recommended by Associate Editor W. Liu. (*Corresponding author: Miloš Grujić.*)

The authors are with imec-COSIC, KU Leuven, 3001 Leuven, Belgium (e-mail: milos.grujic@esat.kuleuven.be; ingrid.verbauwhede@esat.kuleuven.be).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCSI.2022.3158022.

Digital Object Identifier 10.1109/TCSI.2022.3158022

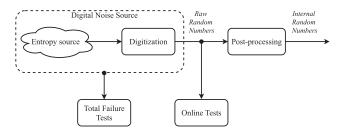

Fig. 1. Architecture of a modern true random number generator.

side-channel attacks (SCA). Among others, the low-latency masking schemes for countering the SCA incur a high area penalty, leaving only limited resources for random number generation [1]. These schemes also require many random bits per execution cycle that a TRNG often cannot provide. Therefore, they resort to faster pseudo-random number generators (PRNGs) to generate random masks [1]. Although producing statistically perfect random bits, the output of a cryptographically secure PRNG becomes entirely predictable once its inner state is leaked or guessed due to its deterministic nature. As it has recently been shown by De Meyer [2], to prevent side-channel leakage of a PRNG and avoid masking PRNG itself, its inner state should be refreshed with truly random bits from a TRNG much more frequently than previously required.

Due to their ubiquity in hardware security, the TRNGs have become subject to rigorous evaluations by the US [3], European [4] and Chinese [5] certification bodies. In addition to passing the statistical tests, modern TRNG designs should have an estimation of the amount of entropy they can provide. Moreover, the TRNG designers should provide a theoretical justification of the unpredictability of its output, as requested by the American NIST SP 800-90B standard [3]. On the other hand, TRNGs for cryptographic applications compliant with the AIS-31 standard [4] should also have a stochastic model from which a lower bound of the Shannon entropy can be estimated.

Fig. 1 illustrates a general TRNG architecture compatible with both the AIS-31 and the NIST SP 800-90B approaches. The entropy source is a component with nondeterministic behavior that exploits an inherently random physical process. The digitization module converts the output of the entropy source, which is often in analog form, into *raw random*

1549-8328 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information. numbers (bits). The entropy source and the digitization module together constitute a digital noise source. The raw random numbers are usually not perfectly unpredictable and need a form of post-processing to increase the unpredictability, measured in entropy per bit, i.e., entropy rate. The random numbers that are output to the user application after the postprocessing are called the internal random numbers (bits). The raw random numbers undergo online tests during the whole operation to detect drops in the entropy and notify the user application. The operation of the digital noise source is closely monitored by the total failure tests, which can immediately detect malfunctioning of the digital noise source and prevent future TRNG outputs. According to the AIS-31, the average Shannon entropy rate of the internal random bits should be higher than 0.997 for the two highest TRNG security classes. On the other hand, NIST SP 800-90B allows claiming a minentropy rate of the internal random bits of up to 0.999 when the arithmetic post-processing is used. Compared to the postprocessing based on cryptographic hash functions or block ciphers, the arithmetic post-processing has the advantage of much lower resource consumption and provides informationtheoretical security when used appropriately.

Although a plethora of TRNG designs have been put forward in the last 20 years, merely a handful of them possess a stochastic model and entropy estimation as a part of the security evaluation [6]–[14]. The throughput and min-entropy estimation of some of the TRNG designs without the stochastic model would likely significantly degrade once their stochastic model has been built. Most TRNG designs with the standardcompliant stochastic models are designed either for high throughput [7], [14] or low area [8], [9], [11]. Since modern TRNGs should not only be used for classical and post-quantum cryptographic applications, but also for providing randomness to the protection mechanisms against the SCA, there is a need for the designs with simultaneously high throughput and low area which are compliant with both AIS-31 and NIST SP 800-90B standards.

To address the lack of low area - high entropy TRNGs with NIST SP 800-90B and AIS-31 compliant stochastic models, this work introduces a new TRNG based on a threeedge ring oscillator with time-to-digital conversion - TROT. Thanks to both efficient entropy generation and optimized post-processing, the TROT offers one of the best area versus throughput trade-offs among previously reported FPGAcompatible TRNGs with a stochastic model. Its digital noise source couples a three-edge mode ring oscillator with a timeto-digital converter (TDC) in a way that enables efficient extraction of the independent white Gaussian jitter present in all three edges. We introduce the stochastic model of the TROT that accounts for the effects of the inherent hardware process variations and employ it to estimate the lower bound on the min-entropy contained in each raw random bit. To increase the min-entropy rate of the internal random bits, we apply the post-processing based on binary linear codes [15]. We propose a throughput optimization method for selecting adequate code and present a compact implementation of the post-processing architecture based on the generator matrix of the chosen code. The TROT produces internal random bits with a min-entropy

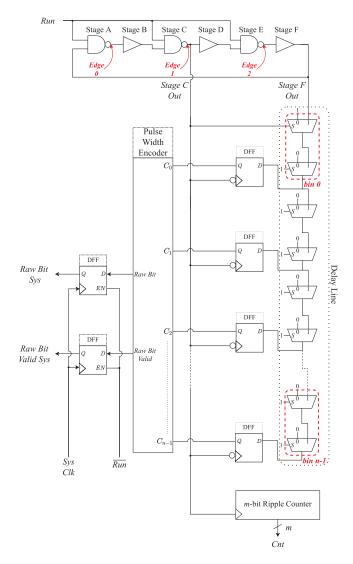

Fig. 2. TROT digital noise source and oscillation counter.

rate of at least 0.999 to fulfill both the AIS-31 and the NIST SP 800-90B entropy requirements. We opted for the minentropy instead of the Shannon entropy rate because the minentropy is the most conservative unpredictability measure. We demonstrate the feasibility of our TRNG on a Xilinx Zynq FPGA device, where the TROT requires relative placement constraints. Our design passes all AIS-31 [4] statistical tests without any cryptographic post-processing.

# II. TROT DIGITAL NOISE SOURCE

The entropy source of the proposed TRNG is a three-edge mode ring oscillator which consists of three inverting and three non-inverting stages, as depicted in the upper part of Fig. 2. Three edges are simultaneously injected by each inverting NAND stage with enable signal *Run*. These edges will have an identical mean period since they propagate through the same stages. The propagation through identical stages significantly reduces the influence of the global and possibly adversarial noise sources, while the local Gaussian noise accumulates independently by each edge. The frequency of the resulting

GRUJIĆ AND VERBAUWHEDE: TROT: THREE-EDGE RING OSCILLATOR BASED TRNG WITH TIME-TO-DIGITAL CONVERSION

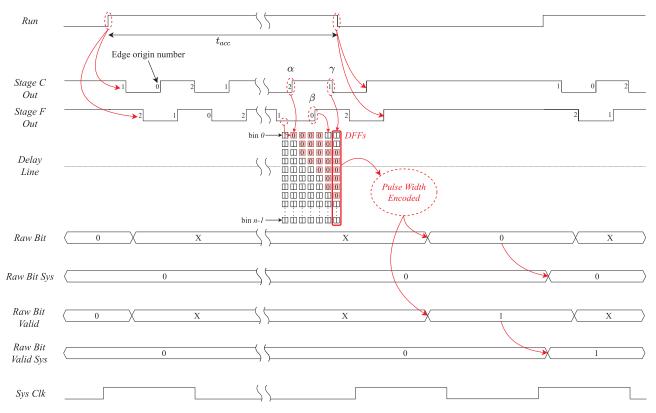

Fig. 3. Timing diagrams of the TROT digital noise source. In this example, the ordered edge triple  $(\alpha, \beta, \gamma)$  corresponds to (2, 0, 1).

ring oscillator signal at the output of any of the six stages will be three times higher than the frequency of a single-edge ring oscillator with the same stages. Due to noise influence, the three edges will inevitably collide, eventually compelling the ring oscillator to a single-edge mode.

A previously proposed TRNG based on the three-edge ring oscillator by Yang et al. [17] extracts randomness by counting the number of oscillations until the collapse of the three-edge mode. Unlike [17], we use a technique based on a single timeto-digital converter (TDC) line as a digitization element to more efficiently exploit the independent timing jitter in each edge. The use of TDC enables higher throughput since the randomness extraction from the three jittery edges can happen much earlier than waiting for the edge collapse. The TDC consists of a delay line formed by high-speed multiplexers and n falling-edge D flip-flops (DFFs) whose D inputs are connected to the outputs of the multiplexers - bins. As seen in Fig. 2, the signal from the third non-inverting stage F is connected to input 1 of the first multiplexer in the delay line. All multiplexers in the delay line have a select signal set to constant 1, except the first, whose select signal comes from the second inverting stage C. The signal from stage C is also used as a clock signal for the DFFs. This oscillator configuration thus falls into a category of multimode multi-phase oscillators, different from the previously proposed single-mode multiphase oscillators [18], [19].

The pulse width encoder is a combinatorial circuit that outputs a raw bit value and a valid signal based on the DFFs' values  $C_0, \ldots, C_{n-1}$ . The raw bit depends on the parity of the number of zeros values relative to the total number of DFFs

and can be logically represented with:

$$Raw Bit = \bigoplus_{i=0}^{n-1} C_i, \tag{1}$$

where n is always even. The raw bit valid signal is set when the first and the last DFF in the TDC have value one, and there is at least one DFF with value zero:

Raw Bit Valid =

$$C_0 \wedge \begin{pmatrix} n-2 \\ \lor \\ i=1 \end{pmatrix} \wedge C_{n-1}.$$

(2)

We use timing diagrams of the digital noise source in Fig. 3 to demonstrate how this configuration of the digital noise source enables capturing the timing jitter effects of all three edges. We denote with  $\alpha$  the last rising edge and with  $\gamma$  the last falling edge at the output of stage C before the oscillations in the ring oscillator are disabled. Similarly, we denote with  $\beta$  the last rising edge at the output of stage F before disabling the ring oscillator. Edges  $\alpha$ ,  $\beta$  and  $\gamma$  thus correspond each to an edge of a different origin -0, 1 or 2, as shown in Fig. 2. The ring oscillator is enabled for time period  $t_{acc}$  by setting the signal Run to 1. The value of  $t_{acc}$  is selected so that all three edges accumulate enough timing jitter during that time, as will be explained in Section III. The propagation of the signal at the output of stage F through the delay line is enabled by the edge  $\alpha$ . Since the signals at the output of stages C and F have approximately 90° phase difference, the signal at the output of stage F will be low and bins in the delay line will start transitioning from 1 to 0, as indicated in Fig. 3. When the edge  $\beta$  appears at the output of stage F, the bins in the delay line that were previously set to 0 by

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS

the edge  $\alpha$  will start transitioning to 1 so that the delay line reflects the state of the signal at the output of stage F. Finally, the edge  $\gamma$  will trigger the corresponding DFFs to sample the state of the delay line. In this manner, the effects of all three edges  $\alpha$ ,  $\beta$  and  $\gamma$  will be captured by the DFFs. The sampled value of the DFFs is then encoded to the raw bit value and the raw bit validity value by the pulse width encoder according to (1) and (2), respectively. After  $t_{acc}$ , the ring oscillator is disabled for one clock cycle. This reset clock cycle ensures independence between consecutive bits and leaves enough time for the pulse width encoder to correctly evaluate the raw bit value and its validity. The ring oscillator is re-enabled on the following rising edge of the clock signal to produce the next random bit and transfer the previous bit and its validity to the system clock domain.

The unavoidable variations of the bins' propagation delays along the delay line will influence the amount of obtainable entropy [20]. While sampling the delay line, the setup or hold time of some DFFs in the TDC might be violated. This event leads to bubbles in the captured TDC code that can be dealt with by bin reordering [7], [21]. To improve the uniformity and minimize bubble manifestations in the TDC, we sacrifice the sampling precision by combining the two adjacent physical bins into one bin of the delay line.

To estimate the jitter accumulated by the three edges and their oscillation period in the design phase, we use an *m*-bit rising edge ripple counter connected to the output of stage C. This counter can also serve as a total failure test to monitor the number of oscillations during the accumulation time  $t_{acc}$ . If the edges collide before the raw random bit is generated due to environmental influences or an attack, the counter will have much lower values than during the regular operation. This observation can be used to raise the alarm to the user application.

# **III. SECURITY ASSESSMENT**

The security assessment provides analytical assurance for the quality of the random bits produced by the digital noise source. Starting from the baseline assumptions about the entropy source and the digitization, we build a stochastic model of the TROT that we use to estimate the min-entropy of the raw random bits.

### A. Notations and Baseline Assumptions

We denote the probability of an event *E* as  $\mathbb{P}(E)$ . The cumulative distribution function and the probability density function of a normally distributed random variable *X* with mean  $\mu_X$  and standard deviation  $\sigma_X$  are denoted as  $F_{\mu_X,\sigma_X}(x)$  and  $f_{\mu_X,\sigma_X}(x)$ , respectively.

The ring oscillator is always sampled in the three-edge mode and the timing jitter affects all three edges. The edges' white Gaussian noise jitter components are mutually independent and their individual observations are independent of each other. Therefore, we only exploit this form of jitter to extract the randomness. The white Gaussian jitter is independent of other noise sources present in the circuit and its variance for each edge grows linearly with time. This increase is characterized by the parameter called jitter strength. Jitter strength is a platform-dependent (chip-dependent) variable and it is obtained empirically as in [21]. We do not extract randomness from timing noise components whose outcomes are correlated at the outputs of stages C and F or any other, possibly correlated and adversarial noise sources, such as power supply or flicker noise, that are present in the circuit. We refer to these components as timing components from the not-exploited noise sources. The not-exploited noise sources might marginally contribute to the total entropy, but they are not used as randomness sources in our model. Thus, the effects of all timing components except the white Gaussian jitter are not removed but instead acknowledged by considering them to be completely deterministic so that a conservative entropy estimation can be provided. However, if the timing influence of the not-exploited noise sources on each edge individually becomes higher than the propagation delay of a single stage of the ring oscillator, the sampled Raw Bit value will not be valid and the Raw Bit Valid signal will stay at 0, thereby detecting invalid mode of operation. In the model, we further account for the realistic non-identical propagation delays of the delay line bins. These propagation delays are also platform-dependent and empirically obtainable [21]. Together with the jitter strength and the edge oscillation period, they are used as input to the stochastic model. We adopt the standard assumption that the raw random bits are independent due to the reset between consecutively generated bits [22], but not necessarily identically distributed.

# B. Stochastic Model

Since the entropy is extracted from the timing jitter of edges  $\alpha$ ,  $\beta$  and  $\gamma$ , we need to model the time of their occurrences relative to the rising edge of the ring oscillator enable signal *Run*. We denote these times with  $t_{\alpha}$ ,  $t_{\beta}$  and  $t_{\gamma}$ , respectively. All three edges will have the same nominal period  $T_{1-RO}$  because all three edges propagate through identical stages. Each  $t_{\alpha}$ ,  $t_{\beta}$  and  $t_{\gamma}$  can correspond to an edge of different origin  $i, j, k \in \{0, 1, 2\}$ , depending on  $t_{acc}$ . Thus, depending on the edge origin, we have:

$$t_{\alpha}^{i} = t_{r \to C}^{i} + \lfloor \frac{t_{acc} - t_{r \to C}^{i}}{T_{1-RO}} \rfloor \cdot T_{1-RO} + t_{\alpha,noise}^{i}, \qquad (3)$$

$$t_{\beta}^{j} = t_{r \to F}^{j} + \lfloor \frac{t_{acc} - t_{r \to F}^{J}}{T_{1-RO}} \rfloor \cdot T_{1-RO} + t_{\beta,noise}^{j}, \qquad (4)$$

$$t_{\gamma}^{k} = t_{f \to C}^{k} + \lfloor \frac{t_{acc} - t_{f \to C}^{k}}{T_{1-RO}} \rfloor \cdot T_{1-RO} + t_{\gamma,noise}^{k}, \quad (5)$$

where  $t_{\{f,r\}\to\{C,F\}}^{\{i,j,k\}}$  is the average time needed for the edge  $\{i, j, k\}$  to propagate as the falling (f) or the rising edge (r) to the output of stage  $\{C, F\}$  for the first time after enabling the ring oscillator, and  $t_{\{\alpha,\beta,\gamma\}noise}^{\{i,j,k\}}$  is the timing component originating from various noise sources in the circuit. The edge origin combination which corresponds to the ordered triple  $(t_{\alpha}, t_{\beta}, t_{\gamma})$  depends on  $t_{acc}$  and this triple can take

the combinations:

$$(t_{\alpha}, t_{\beta}, t_{\gamma}) = \begin{cases} I) (t_{\alpha}^{a}, t_{\beta}^{1}, t_{\gamma}^{2}), & \text{if } t_{acc} \in \\ (t_{f \to C}^{2} + j \cdot T_{1-RO} + t_{\gamma,noise}^{2}, \\ t_{f \to C}^{0} + j \cdot T_{1-RO} + t_{\gamma,noise}^{0}); \\ II) (t_{\alpha}^{1}, t_{\beta}^{2}, t_{\gamma}^{0}), & \text{if } t_{acc} \in \\ (t_{f \to C}^{0} + j \cdot T_{1-RO} + t_{\gamma,noise}^{0}, \\ t_{f \to C}^{1} + (j+1) \cdot T_{1-RO} + t_{\gamma,noise}^{1}); \\ III) (t_{\alpha}^{2}, t_{\beta}^{0}, t_{\gamma}^{1}), & \text{if } t_{acc} \in \\ (t_{f \to C}^{1} + (j+1) \cdot T_{1-RO} + t_{\gamma,noise}^{1}, \\ t_{f \to C}^{2} + (j+1) \cdot T_{1-RO} + t_{\gamma,noise}^{1}); \end{cases}$$

where  $j \in \mathbb{Z}^+$ . The first two terms in (3) – (5) are not noise dependent and we replace them with a single term  $\mu_{nom,\{\alpha,\beta,\gamma\}}^{\{i,j,k\}}$ . The timing components originating from the noise sources can be decomposed into a component originating from the not-exploited noise sources and a component originating from the exploited zero-mean white Gaussian noise sources –  $t_{\{\alpha,\beta,\gamma\},G}^{\{i,j,k\}}$ . The not-exploited noise sources will further be treated as deterministic –  $t_{\{\alpha,\beta,\gamma\},det}^{\{i,j,k\}}$ , representing the worst-case scenario. Hence (3) – (5) can be rewritten in a consolidated manner as:

$$t_{\{\alpha,\beta,\gamma\}}^{\{i,j,k\}} = \mu_{nom,\{\alpha,\beta,\gamma\}}^{\{i,j,k\}} + t_{\{\alpha,\beta,\gamma\},det}^{\{i,j,k\}} + t_{\{\alpha,\beta,\gamma\},G}^{\{i,j,k\}}.$$

(6)

The expected values of the times of the occurrences of the edges  $\alpha$ ,  $\beta$  and  $\gamma$  for a given  $t_{acc}$  are:

$$\mu_{\{\alpha,\beta,\gamma\}}(t_{acc}) = \mathbb{E}[t_{\{\alpha,\beta,\gamma\}}^{\{i,j,k\}}] = \mu_{nom,\{\alpha,\beta,\gamma\}}^{\{i,j,k\}} + \mathbb{E}[t_{\{\alpha,\beta,\gamma\},det}^{i,j,k}].$$

(7)

Since the white Gaussian noise is independent of the notexploited noise sources and the not-exploited sources are considered to be deterministic, for the variances of the times of the edge occurrences we have:

$$\sigma^{2}_{\{\alpha,\beta,\gamma\}}(t_{acc}) = \sigma^{2}[t^{\{i,j,k\}}_{\{\alpha,\beta,\gamma\}}] = \sigma^{2}[t^{\{i,j,k\}}_{\{\alpha,\beta,\gamma\},G}].$$

(8)

Given that the variances of the white Gaussian noise increase linearly with time and  $\mu_{nom,\gamma}^k > \mu_{nom,\beta}^j > \mu_{nom,\alpha}^i$ , it holds:

$$\sigma^2[t^k_{\gamma,G}] > \sigma^2[t^j_{\beta,G}] > \sigma^2[t^i_{\alpha,G}].$$

(9)

Thus, to simplify the stochastic model, without loss in conservatism, we set  $\sigma_{\gamma}^2(t_{acc}) = \sigma_{\beta}^2(t_{acc}) = \sigma_{\alpha}^2(t_{acc}) = \sigma_{min}^2(t_{acc})$ , where  $\sigma_{min}^2$  is the lower bound on the white Gaussian noise variance of the edge  $\alpha$  for the accumulation time  $t_{acc}$ . This simplification helps us avoid using the exact values of each stage's rising and falling edge propagation delays, which are usually not equal and cannot be precisely determined. The value of  $\sigma_{min}^2$  can be calculated from the knowledge of the platform jitter strength  $J_S$ , the oscillation period of a single edge  $T_{1-RO}$  and the smallest number of periods of the edge *i* that corresponds to the edge  $\alpha$ . This number can be obtained from  $Cnt(t_{acc})$  – the value of the ripple counter after  $t_{acc}$ . The  $\sigma_{min}^2$  value can be determined as:

$$\sigma_{min}^2(t_{acc}) = J_S \cdot \left( \lceil * \rceil \frac{Cnt(t_{acc}) - 1}{3} - 1 \right) \cdot T_{1-RO}.$$

(10)

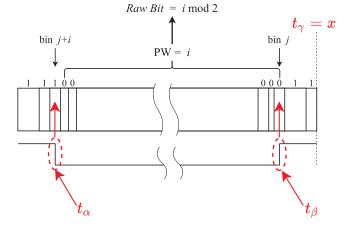

Fig. 4. Modeling of the digitization – determining PW = i.

The TDC and the pulse width encoder map relative positions of the edges  $\alpha$  and  $\beta$  to the edge  $\gamma$  into a random bit. At the sampling moment, the bins in the delay line will contain a string of zeros encircled by bins with strings of ones - a pulse, as illustrated in Fig. 3. If there are no 0 bins or if the first and the last bin do not have value 1, the raw bit validity signal will have value 0 and the raw bit value will be discarded. We refer to the number of 0s in the delay line as the pulse width (PW). The PW can have any value between 1 and n - 2, where n is the total number of bins. For the odd PW values, the pulse width encoder outputs 1, and 0 for the even values. Therefore, we calculate the probabilities of all possible PW values to determine the probability of each encoder output. For a given position of the edge  $\gamma$ , we first calculate the probability that the pulse with starting position in bin j will have a width of *i* bins, as depicted in Fig. 4:

$$\mathbb{P}(PW_j = i|t_{\gamma} = x)$$

=  $\mathbb{P}(t_{\beta} \in \text{bin } (j)|t_{\gamma} = x)$

$\cdot \mathbb{P}(t_{\alpha} \in \text{bin } (j+i)|t_{\gamma} = x).$  (11)

To remove the condition on the starting position bin, we sum (11) over all possible valid positions j:

$$\mathbb{P}(PW = i|t_{\gamma} = x)$$

=  $\sum_{j=1}^{n-i-1} \mathbb{P}(t_{\beta} \in \text{bin } (j)|t_{\gamma} = x)$

$\cdot \mathbb{P}(t_{\alpha} \in \text{bin } (j+i)|t_{\gamma} = x).$  (12)

The condition on the position of the edge  $\gamma$  can be removed by integrating out normally distributed  $t_{\gamma}$ :

$$\mathbb{P}(PW = i)$$

$$= \int_{-\infty}^{+\infty} \sum_{j=1}^{n-i-1} \mathbb{P}(t_{\beta} \in \text{bin } (j)|t_{\gamma} = x) \cdot \mathbb{P}(t_{\alpha} \in \text{bin } (j+i)|t_{\gamma} = x)$$

$$\cdot f_{\mu_{\gamma},\sigma_{min}}(x) \, dx.$$

(13)

We use  $d_{f,i}$  and  $d_{r,i}$  to denote  $1 \to 0$  and  $0 \to 1$  propagation delays of the bin *i*, respectively. To simplify the notation, we also introduce  $d_{r,k}^{\Sigma} = \sum_{i=0}^{k} d_{r,i}$  and  $d_{f,k}^{\Sigma} = \sum_{i=0}^{k} d_{f,i}$ .

6

Then we can rewrite the bin probabilities for  $t_{\alpha}$  and  $t_{\beta}$  as functions of their distances to  $t_{\gamma} = x$ :

$$\mathbb{P}(t_{\alpha} \in \operatorname{bin}(j+i)|t_{\gamma} = x) = \mathbb{P}(x - d_{f,j+i}^{\Sigma} < t_{\alpha} < x - d_{f,j+i-1}^{\Sigma}), \quad (14)$$

$$\mathbb{P}(t_{\theta} \in \operatorname{bin}(j)|t_{\theta} = x)$$

$$P(t_{\beta} \in \text{bin}(j)|t_{\gamma} = x) = \mathbb{P}(x - d_{r,j}^{\Sigma} < t_{\beta} < x - d_{r,j-1}^{\Sigma}).$$

(15)

By substituting (14) and (15) in (13) and using the fact that exploited jitter components are normally distributed, we obtain:

$$\mathbb{P}(PW = i)$$

$$= \int_{-\infty}^{+\infty} \sum_{j=1}^{n-i-1} \left[ F_{\mu_{\beta},\sigma_{min}}(x - d_{r,j-1}^{\Sigma}) - F_{\mu_{\beta},\sigma_{min}}(x - d_{r,j}^{\Sigma}) \right]$$

$$\cdot \left[ F_{\mu_{\alpha},\sigma_{min}}(x - d_{f,j+i-1}^{\Sigma}) - F_{\mu_{\alpha},\sigma_{min}}(x - d_{f,j+i}^{\Sigma}) \right]$$

$$\cdot f_{\mu_{\gamma},\sigma_{min}}(x) \ dx. \tag{16}$$

Since the PW encoding to a raw random bit is used only when the pulse is captured in the TDC, we need to calculate the probability of a specific PW value given that a pulse of any width has been registered in the TDC. We use the capital letter Q to denote the event when the pulse formed by edges  $\alpha$  and  $\beta$  is captured in the TDC and its width is at least one TDC bin. The probability of this event is:

$$\mathbb{P}(Q) = \sum_{i=1}^{n-2} \mathbb{P}(PW = i).$$

(17)

Finally, the probability of PW being *i* bins given that the TDC correctly captured a pulse is:

$$\mathbb{P}(PW = i \mid Q) = \frac{\mathbb{P}(PW = i)}{\sum_{i=1}^{n-2} \mathbb{P}(PW = i)}.$$

(18)

# C. Entropy Estimation of the Raw Random Numbers

The raw random bit is obtained by XOR-ing together outputs of all DFFs in the TDC. Therefore, the binary probabilities are computed by summing the probabilities of all odd pulse widths for bit 1 and all even pulse widths for bit 0:

$$\mathbb{P}(b=l) = \sum_{i=1}^{\frac{n}{2}-1} \mathbb{P}(PW = 2i - l \mid Q), \quad l \in \{0, 1\}.$$

(19)

Since each bit is produced after restarting the TRNG and thus assumed to be independent of previous and future outputs, the min-entropy rate of raw random bits can be directly calculated by substituting (16), (18) and (19) in:

$$H_{\infty}^{raw} = -\log_2(max(\mathbb{P}(b=1), \mathbb{P}(b=0))).$$

(20)

Alternatively, the Shannon entropy rate can be calculated as:

$$H_1^{raw} = -\sum_{i=0}^{1} \mathbb{P}(b=i) \cdot \log_2(\mathbb{P}(b=i)).$$

(21)

To make a conservative min-entropy estimation claim, besides experimentally obtained  $J_S$ ,  $T_{1-RO}$  and bin propagation delays, we must make additional assumptions on the relations of the values  $\mu_{\alpha}$ ,  $\mu_{\beta}$  and  $\mu_{\gamma}$  in (16). These values cannot be precisely determined at the design time due to the influence of the operating conditions, the power supply noise and notexploited correlated local noise sources. From (3) - (5) and (7), we have  $\mu_{nom,\gamma}^k - \mu_{nom,\beta}^j \approx d_{RO\,stage}$  and  $\mu_{nom,\beta}^j - \mu_{nom,\alpha}^i \approx d_{RO\,stage}$ , where  $d_{RO\,stage}$  is the average stage delay of the ring oscillator. Therefore, we restrict the difference between  $\mu_{\alpha}$ ,  $\mu_{\beta}$  and  $\mu_{\gamma}$  to be at least  $d_{RO stage/2}$  in the model. This restriction is justified because the correlated noise sources will have a relatively small influence compared to the white Gaussian noise for small  $t_{acc}$  and because the impact of the power supply noise will be reduced due to its equal influence on all three edges, as previously also observed by [8], [17], [23]. We analyze the effects of  $\mu_{\alpha}$ ,  $\mu_{\beta}$  and  $\mu_{\gamma}$  on the min-entropy to determine its conservative lower bound  $H^{raw}_{\infty \ lb}$ in Section IV.

# IV. IMPLEMENTATION OF THE DIGITAL NOISE SOURCE AND APPLICATION OF THE STOCHASTIC MODEL

To demonstrate the feasibility of the design and confirm the conservativeness of the min-entropy estimation, we implement the TROT digital noise source in a Xilinx Zynq-7000 FPGA device. We first measure our FPGA chip platformspecific parameters and then apply the stochastic model to determine the lower bound on the min-entropy of the raw random bits  $H_{\infty,lb}^{raw}$ . Platform-specific parameters are the jitter strength, the propagation delays of the bins in the delay line and the ring oscillator's period in the three-edge mode. Since these parameters are crucial for the correct entropy assessment, they have to be correctly measured before the TRNG is implemented. We chose the system clock period to be  $T_{CLK} = 8$  ns, and we measured the white Gaussian noise jitter strength of  $J_S = 9.7$  fs on our platform using adapted on-chip differential TDC methodology from [21] with identical routing. The dependence of  $H_{\infty,lb}^{raw}$  on the amount of accumulated jitter is used to determine the optimal postprocessing construction in Section V.

# A. Entropy Source

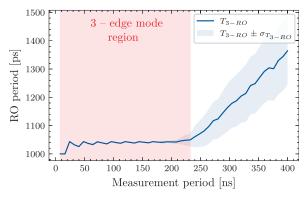

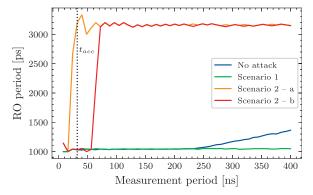

Each ring oscillator stage is implemented using one lookup table (LUT), while the complete ring oscillator consists of six symmetrically placed LUTs. For the design phase, we used a 9-bit ripple counter at the output of stage C to measure the average period of the ring oscillator. We further monitor its evolution with the increase of the measurement time, as shown in Fig. 5. Measurements are performed in steps of  $T_{CLK}$ , and for each step, we repeat the experiment  $10^5$  times. We observe that for periods higher than 232 ns, the edges in the ring oscillator start colliding, leading the ring oscillator out of the three-edge oscillation mode. This effect can be noted by the sharp rise of the ring oscillator period curve and the increase of its standard deviation. Consequently, the accumulation time  $t_{acc}$  has to be lower than 232 ns for the correct operation of the TROT. For the average period of the ring oscillator in the three-edge mode we obtained

Fig. 5. Evolution of the oscillation period of the ring oscillator  $-T_{3-RO}$ .

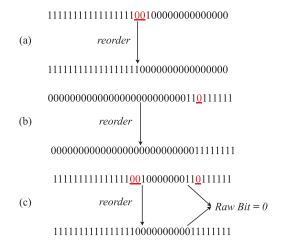

Fig. 6. Examples of bubbles and bin reordering in TDC during: a) rising edge propagation, and b) falling edge propagation during TDC characterization; c) equivalence of ordered and unordered TDC during pulse propagation.

$T_{3-RO} = 1042.57$  ps and the oscillation period of a single edge is  $T_{1-RO} = 3 \cdot T_{3-RO} = 12 \cdot d_{RO stage} = 3127.7$  ps.

#### B. Time-to-Digital Converter and Pulse Width Encoder

The delay line is implemented using multiplexer stages of cascaded CARRY4 primitives. The two consecutive stages of each CARRY4 are combined in one bin to decrease the nonuniformity of the bins' propagation time, which has a negative impact on the min-entropy of the TDC-based TRNGs [20]. To measure the propagation delays of the bins, we used the Monte Carlo methodology proposed in [21]. As mentioned in Section II, the captured TDC code will contain bubbles - the occurrences of one or more 0-bins in array of consecutive 1s or the occurrence of one or more 1-bins in array of consecutive 0s. During the propagation delay measurements, the bubbles are handled on the PC by reordering the bins to obtain strings of consecutive 0s and 1s, as depicted in Fig. 6a and Fig. 6b. This procedure is done for every TDC code sample which contains bubbles, but only during the measurements of the bins' delays. On the other hand, as shown by the example in Fig. 6c, the pulse width encoder transforms the width of the captured pulse into one bit, depending only on the parity of the numbers of 0-bins. Thus, the same value is output for both the unordered and ordered TDC bins. This observation implies that the bin reordering is unnecessary

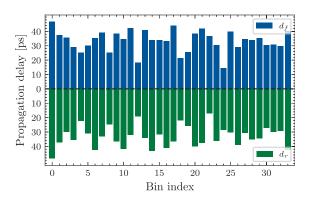

Fig. 7. Characterization of bins in the delay line.

during the TDC operation in TROT since the pulse width encoding into a raw bit is bubble-proof. The obtained rising  $(d_r)$  and falling  $(d_f)$  delays of the bins are depicted in Fig. 7. Many different calibration techniques have been reported to improve the linearity of the delay line based TDCs [24]-[27]. However, these techniques require hundreds or even thousands of additional LUTs and DFFs. Due to these prohibitively high implementation costs, we chose to instead include bin-to-bin non-linearities in the stochastic model and account for their effect on the lower bound of entropy produced by the TROT digital noise source. Namely, we use individual bin delays in equation (16) in Section III and do not assume that the mean edge position can be precisely determined. The mean edge position is further impacted by various noise sources that are always present but not used in our design. The influence of TDC non-linearity and imprecise mean edge assessment are examined in Subsection IV-C. The number of bins in the delay line needs to be selected such that the total propagation delay for both edges is at least equal to the average period of the ring oscillator in the three-edge mode  $T_{3-RO}$ . This condition is satisfied when the delay line has at least 33 bins for our implementation. Since two bins are implemented by one CARRY4, we use 34 bins in 17 CARRY4 primitives and 34 DFFs in the corresponding slices.

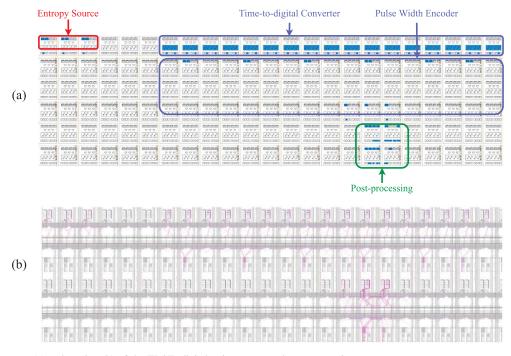

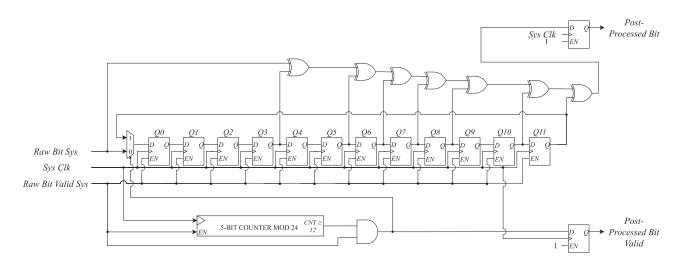

The pulse width encoder is realized as a combinatorial circuit for equations (1) and (2) in Section II, and it can be implemented using 15 LUTs. In addition, two DFFs are used to transfer the raw bit value and its validity signal to the system clock domain. Our implementation of the digital noise source required relative placement constraints for symmetrical placement of the ring oscillator stages and for CARRY4 primitives and their corresponding DFFs in FPGA slices above the ring oscillator. The TROT digital noise source fits in 29 slices and its FPGA placement and routing are illustrated in Fig. 8.

### C. Stochastic Model Application

By applying the stochastic model and using measured platform-specific parameters, we can numerically calculate the min-entropy for any time difference between  $\mu_{\alpha}$ ,  $\mu_{\beta}$  and  $\mu_{\gamma}$ , and for different values of the accumulated timing jitter. In this manner, we are also taking into consideration the influence of the not-exploited noise sources on the estimated

Fig. 8. FPGA placement (a) and routing (b) of the TROT: digital noise source and post-processing.

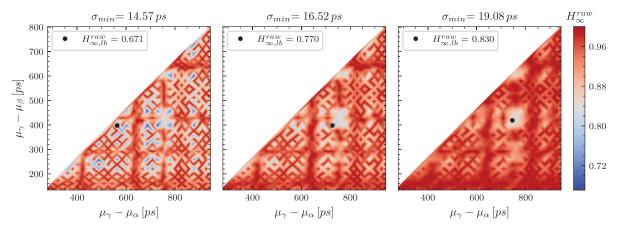

Fig. 9. Dependency of  $H_{\infty}^{raw}$  on the position of the edges in the TDC line for three different values of the accumulated jitter corresponding to accumulation times 24 ns, 32 ns and 40 ns.

min-entropy. The lower bound on the min-entropy  $H_{\infty,lb}^{raw}$  is then obtained by finding the global minimum for each value of the given jitter. Fig. 9 presents the min-entropy estimation as a function of the time distances of  $\mu_{\alpha}$  and  $\mu_{\beta}$  to  $\mu_{\gamma}$  for three different amounts of the jitter, where global minima are marked with black dots. We observe that the TDC's nonuniformity indeed significantly impacts the min-entropy and that the position of the global minimum is dependent on the amount of accumulated jitter, i.e., accumulation time. This observation confirms the necessity of including individual bin propagation delays in the stochastic model.

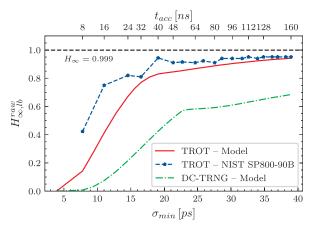

Fig. 10 shows the dependence of the min-entropy's lower bound estimation on the accumulated jitter on the lower x-axis and corresponding accumulation times on the upper x-axis. It can be observed that the min-entropy exhibits a rapid increase for the accumulation times up to 40 ns. For longer accumulation times, the growth tapers off because the non-uniformity of the TDC cannot be overcome even with a considerably higher variance of timing jitter. To confirm the validity of the min-entropy estimations, we applied the entropy estimators from NIST SP 800-90B [3] on the raw random bit sequences obtained for 20 different values of  $t_{acc}$  between 8 ns and 160 ns in steps of  $T_{CLK} = 8$  ns. The reported results are also presented in Fig. 10. As expected, the min-entropy estimation is always lower than NIST SP 800-90B estimations due to our conservative stochastic model.

# D. Comparison With the DC-TRNG

The DC-TRNG [7] is another TRNG design with a stochastic model that also uses time-to-digital conversion for extracting randomness from the ring oscillator jittery edge. Unlike TROT, the DC-TRNG uses a regular one-edge ring oscillator as the entropy source and the time-to-digital converter

Fig. 10. Dependency of the lower bound of the  $H_{\infty}^{raw}$  on the amount of the accumulated jitter / accumulation time for the TROT and the DC-TRNG.

to sample the ring oscillator signal by using the system clock after enough white noise jitter has been accumulated. To show the advantage of the TROT design over the DC-TRNG, we estimate its lower bound on the min-entropy of the raw random bits when the DC-TRNG is implemented using identical FPGA resources as the TROT. The dependency of the entropy bound estimation on the accumulation time is also shown in Fig. 10. It can be observed that the min-entropy bound of the TROT grows significantly faster for shorter accumulation times and it remains constantly higher than the min-entropy bound of the DC-TRNG for longer accumulation times.

# V. POST-PROCESSING CONSTRUCTION

#### A. Entropy Estimation of the Internal Random Numbers

As shown in Section IV, the min-entropy of the digital noise source very slowly approaches the desired bound of  $H_{\infty}^{int} =$ 0.999. Thus, to increase the min-entropy while maintaining high throughput and low implementation cost, we opt to use post-processing based on the binary linear codes [15]. This post-processing represents a generalization of the commonly used XOR post-processing – parity filter. To explain it, we start with a theorem that gives the relation between the min-entropy of the random bits post-processed by any vectorial Boolean function and maximal one-dimensional bias of its output.

**Theorem 1:** (follows from [15]) Let  $F : \mathbb{F}_2^n \to \mathbb{F}_2^k$ be a vectorial Boolean function with coordinate functions  $(f_0, \ldots, f_{k-1}) : \mathbb{F}_2^n \to \mathbb{F}_2$  and  $\delta_{max}$  maximal one-dimensional bias of its output, defined as  $\delta_{max} = \max_{u \in \mathbb{F}_2^k \setminus \{0\}} \left| \mathbb{P}\left( \sum_{i=0}^{k-1} u_i f_i(x) = 1 \right) - 0.5 \right|$ . Then, the minentropy rate of the output of F is greater or equal to:

$$1 - \log_{2^k} (1 + 2^{k+1} \cdot \delta_{max}). \tag{22}$$

It was also proved in [15] that the min-entropy rate of the output bits of *F* is at least  $1 - \log_{2^k}(1 + 2^{k+d} \cdot e^d)$  when *F* is defined by  $F(x) = \mathbf{G} \cdot \mathbf{x}$ . Here,  $\mathbf{G}$  is  $k \times n$  generator matrix of a [n, k, d] linear code and all *n* bits of  $\mathbf{x} = (x_0, \dots, x_{n-1})$  are independent and identically distributed (IID) with constant bias  $e = |\mathbb{P}(x_i = 1) - 0.5|$ . In contrast to commonly used Von Neumann's debiasing that outputs perfectly unbiased bits

but requires IID inputs, this post-processing construction does not require identically distributed bits. With the knowledge of the lower bound on the min-entropy of the raw random bits produced by the TROT, the min-entropy rate of the internal random bits obtained by post-processing with a generator matrix of a linear code can be bounded from below. To this end, we give and prove the following proposition based on Theorem 1.

**Proposition 1:** Let  $\mathbf{x} = (x_0, \ldots, x_{n-1})$  be a sequence of independent but not necessarily identically distributed bits produced by a digital noise source with min-entropy per bit of at least  $H_{\infty,lb}^{raw}$ . Then, for the min-entropy rate of the output bits  $H_{\infty}^{int}$  of the post-processing function  $F(x) = \mathbf{G} \cdot \mathbf{x}$ , where  $\mathbf{G}$  is generator matrix of a [n, k, d] linear code, it holds:

$$H_{\infty}^{int} \ge 1 - \log_{2^k} (1 + (2^{1 - H_{\infty,lb}^{raw}} - 1)^d \cdot 2^k).$$

(23)

*Proof:* Since the *i*<sup>th</sup> coordinate function of F(x) corresponds to the inner product of the *i*<sup>th</sup> row of G and *n*-bit vector x, every  $f_i(x)$  is a modulo-2 sum of at least d bits of x, by definition of the generator matrix G of the linear code with minimum distance d [15]. The inner product  $\sum_{i=0}^{k-1} u_i f_i(x)$  is also a sum of at least d bits of x for all  $u \in \mathbb{F}_2^k \setminus \{0\}$ , since any non-zero sum of the codewords of a linear code is also a codeword with minimum Hamming weight d. Let  $\mathcal{I}_u$  be a set of all indices of x such that  $\sum_{i=0}^{k-1} u_i f_i(x) = \bigoplus_{i \in \mathcal{I}_u} x_i$  for  $u \in \mathbb{F}_2^k \setminus \{0\}$ . Then, the one-dimensional bias of  $\sum_{i=0}^{k-1} u_i f_i(x)$  can be computed by applying the piling-up lemma [28]:

$$\delta_u = \left| \mathbb{P}\left( \sum_{i=0}^{k-1} u_i f_i(x) = 1 \right) - \frac{1}{2} \right| = 2^{|\mathcal{I}_u| - 1} \cdot \prod_{i \in \mathcal{I}_u} e_i,$$

where  $e_i$  is bias of the bit  $x_i$ . Given that the lower bound on the min-entropy per input bit is known and all bits of x are independent,  $e_i$  can be bounded from above  $e_i \leq 2^{-H_{\infty,lb}^{raw}} - \frac{1}{2}$ . By using this inequality and the fact that by the definition of  $\mathcal{I}_u$ , the cardinality of  $\mathcal{I}_u$  is at least d for all  $u \in \mathbb{F}_2^k \setminus \{0\}$ , we obtain:

$$\delta_u \le \delta_{max} \le 2^{d-1} \cdot \left(2^{-H_{\infty,lb}^{raw}} - \frac{1}{2}\right)^d.$$

(24)

Finally, substituting the bound on  $\delta_{max}$  from (24) in (22) of Theorem 1 leads to (23).

## B. Throughput Optimization

The final throughput of the TROT after post-processing with the generator matrix of a linear code with code rate k/n is computed as:

$$TP = \frac{k}{n} \cdot \frac{1}{t_{acc} + T_{CLK}} \cdot 1 \, bit, \qquad (25)$$

To optimize the throughput, we need to properly select the code such that  $H_{\infty}^{int} \ge 0.999$  holds for given  $H_{\infty,lb}^{raw}$ .

High values of (25) are obtained with codes that have both high k/n and need low  $H^{raw}_{\infty,lb}$ , i.e., low  $t_{acc}$ . We start our optimization procedure with a list of 32 896 best known binary linear codes from [29]. For each code, we determine the minimum necessary  $H^{raw}_{\infty,lb}$  needed to achieve  $H^{int}_{\infty} \geq$ 0.999 by (23) and the code rate k/n. We then classify a code

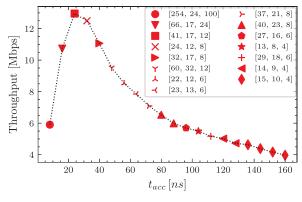

Fig. 11. Expected throughput after post-processing with the generator matrix of a suitable linear code for different accumulation times and  $H_{\infty}^{int} \ge 0.999$ .

as *suitable* if: (i) among all codes with the same k/n, it has the lowest minimum necessary  $H_{\infty,lb}^{raw}$ ; (ii) among all codes with same minimum necessary  $H_{\infty,lb}^{raw}$ , it has the highest k/n; (iii) all other suitable codes with higher k/n have higher minimum necessary  $H_{\infty,lb}^{raw}$ . The set of suitable codes will contain codes that best meet both the high code rate and the low minimum necessary  $H_{\infty,lb}^{raw}$  criteria. The obtained 468 suitable codes are sorted in descending order of their minimum necessary  $H_{\infty,lb}^{raw}$ . Then, as in Fig. 10, for 20 different  $t_{acc}$ values between 8 ns and 160 ns in steps of  $T_{CLK}$ , we calculate  $H_{\infty,lb}^{raw}$ , and for each value we select the first suitable code from the sorted list with a lower minimum necessary  $H_{\infty,lb}^{raw}$ . Fig. 11 presents maximum achievable throughput by (25) for different accumulation times and obtained suitable codes. The highest throughput of 12.957 *Mbps* is achieved for  $t_{acc} = 24$  ns by post-processing with the generator matrix of [41, 17, 12] code, while the second-highest throughput of 12.5 Mbps is achieved with the generator matrix of the [24, 12, 8] code for  $t_{acc} = 32$  ns. For  $t_{acc} > 160$  ns, the throughput continues to fall under 4 Mbps.

# C. Custom Post-Processing Architecture

The [41, 17, 12] code is not cyclic, and thus it does not have a generator polynomial that can be used for efficient hardware implementation. However, if we somewhat sacrifice the throughput, an efficient hardware implementation can be achieved with [24, 12, 8] Golay code. We first apply elementary transformations on the standard form of its generator matrix  $G_S$ :

| Г           | 1               | 1                                                                                    | 0                                                                                                                                      | 1                                                                                                                                                                              | 1                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 -                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                 | -                                                                                    |                                                                                                                                        |                                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | Ŭ               | -                                                                                    | -                                                                                                                                      | ~                                                                                                                                                                              | -                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | 0               |                                                                                      | 0                                                                                                                                      | 1                                                                                                                                                                              |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | 1               | 0                                                                                    | 0                                                                                                                                      | 0                                                                                                                                                                              | 1                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| т           | 0               | 1                                                                                    | 0                                                                                                                                      | 0                                                                                                                                                                              | 0                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>I</b> 12 | 1               | 0                                                                                    | 1                                                                                                                                      | 0                                                                                                                                                                              | 0                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |